## Parallel efficient algorithms and their programming.

## Fundation of ATHAPASCAN-1.

Jean-Louis Roch LMC-IMAG Projet CNRS-INPG-UJF-INRIA APACHE BP 53X 100, rue des Mathématiques 38041 Grenoble Cedex 9, France Email: [Jean-Louis.Roch]@imag.fr

October 17, 1997

Ce rapport contient les deux premiers chapitres du tutoriel "Parallel Computer Algebra" donné au colloque annuel de calcul formel ISSAC (Juillet 97, Hawaii) par Jean-Louis Roch et Gilles Villard. Il décrit les bases pour la construction, l'analyse et la programmation d'algorithmes parallèles sur des architectures distribuées. Utilisant les techniques à la base de l'algorithmique parallèle synchrone PRAM, il montre comment elles peuvent être appliquées à la construction d'algorithmes parallèles qui conduisent à des programmes performants sur des architectures distribuées asynchrones. Deux points sont alors critiques: la prise en compte des surcoûts de communication et d'ordonnancement.

Le premier chapitre présente les techniques permettant la construction d'algorithmes *efficaces*. Différents critères doivent être minimisés: le nombre d'opérations qui doit rester proche du nombre optimal d'opérations sur une machine séquentielle, le temps parallèle minimal (i.e. sur un nombre infini de processeurs) pour permettre que le temps d'exécution diminue lorsque le nombre de processeurs augmente (on parle d'extensibilité), le volume de communications pour limiter leur surcoût sur une architecture distribuée. Pris séparément, ces différents critéres conduisent à des algorithmes fondamentalement différents. Un algorithme efficace doit alors réaliser un bon compromis entre ces critères, pris deux à deux ou dans leur ensemble; il est souvent basé sur un couplage entre ces différents algorithmes: on parle de *poly-algorithmes* ou d'*algorithmes en cascade*.

Différents exemples illustrent les techniques de base pour construire des algorithmes efficaces réalisant des compromis intéressants. Les algorithmes sont représentés par des graphes de flots de données. Leur programmation est explicitée à partir d'un langage abstrait, ATH (Asynchronous Tasks Handling).

Le deuxième chapitre étudie l'ordonnancement de tels algorithmes sur une architecture distribuée asynchrone (modèle LogP). Le cas le plus général où le graphe est inconnu (les tâches qui le constituent sont construites en cours d'exécution et sont de durées inconnues) est spécifiquement étudié. Un algorithme d'ordonnancement en-ligne qui assure des exécutions optimales pour un algorithme parallèle efficace tel ceux étudiés dans le chapitre 1 est explicité. En conclusion, le langage ATHAPASCAN qui permet l'implémentation d'un tel ordonnancement est présenté. Ce langage (implémenté par une bibliothèque C++) est une réalisation concrète du langage ATH.

# **Chapter 1**

# **Parallel efficient algorithms**

### Contents

| 1.1        | PRAN                                                     | A, DFG and cost analysis                                                                                                                                                                                                                 |

|------------|----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            | 1.1.1                                                    | The PRAM model                                                                                                                                                                                                                           |

|            | 1.1.2                                                    | Execution of a PRAM program and data-flow graphs                                                                                                                                                                                         |

|            | 1.1.3                                                    | Describing PRAM algorithms: ATH language                                                                                                                                                                                                 |

|            | 1.1.4                                                    | Time, work and communication costs                                                                                                                                                                                                       |

|            | 1.1.5                                                    | Efficient algorithms                                                                                                                                                                                                                     |

|            | 1.1.6                                                    | Example                                                                                                                                                                                                                                  |

|            | 1.1.7                                                    | Relations between PRAMs 13                                                                                                                                                                                                               |

| 1.2        | Increa                                                   | asing granularity                                                                                                                                                                                                                        |

|            | 1.2.1                                                    | Parallel divide and conquer                                                                                                                                                                                                              |

|            | 1.2.2                                                    | Minimizing communication work                                                                                                                                                                                                            |

|            | 1.2.3                                                    | Conclusion                                                                                                                                                                                                                               |

| 1.3        | Redur                                                    | ndancy and cascading divide&conquer                                                                                                                                                                                                      |

|            | 1.3.1                                                    | DFG of the best sequential algorithm                                                                                                                                                                                                     |

|            | 1.3.2                                                    | Breaking dependencies                                                                                                                                                                                                                    |

|            | 1.3.3                                                    |                                                                                                                                                                                                                                          |

|            | 1.5.5                                                    | Cascading divide&conquer to minimize time                                                                                                                                                                                                |

|            | 1.3.4                                                    | Cascading divide&conquer to minimize time       20         Applications in linear algebra       22                                                                                                                                       |

|            |                                                          |                                                                                                                                                                                                                                          |

| 1.4        | 1.3.4<br>1.3.5                                           | Applications in linear algebra                                                                                                                                                                                                           |

| 1.4        | 1.3.4<br>1.3.5                                           | Applications in linear algebra    22      Conclusion    22                                                                                                                                                                               |

| 1.4        | 1.3.4<br>1.3.5<br><b>Rand</b>                            | Applications in linear algebra    22      Conclusion    22      comization to decrease time or preserve work.    23                                                                                                                      |

| 1.4        | 1.3.4<br>1.3.5<br><b>Rand</b><br>1.4.1                   | Applications in linear algebra       22         Conclusion       22 <b>omization to decrease time or preserve work.</b> 23         Randomization to suppress dependencies       23                                                       |

| 1.4<br>1.5 | 1.3.4<br>1.3.5<br><b>Rand</b><br>1.4.1<br>1.4.2<br>1.4.3 | Applications in linear algebra       22         Conclusion       22 <b>comization to decrease time or preserve work.</b> 23         Randomization to suppress dependencies       23         Randomization to provide efficiency       25 |

Parallel algorithmic is a successful theory. Several methods, techniques and paradigms, which are presented in several books and surveys [60, 5, 30, 38, 35, 20, 41, 28, 39, 45] have been developed to build powerful theoretical algorithms. Furthermore, they stand as a basis for implementation of performant programs on effective parallel architectures. Those general techniques overflow computer algebra framework even if arithmetic and algebraic computations are of specific interest.

In this chapter, we introduce the main techniques involved in the building of parallel algorithms. They are illustrated on elementary computer algebra problems. The underlying model is PRAM but the data-flow graph representation is also introduced. It is used to describe executions of a parallel algorithm and to define its cost. Three factors are here preponderant: parallel execution time, number of operations and granularity which is related to the required volume of communications. An efficient algorithm realizes a compromise solution between those three factors.

The organization of the chapter is as follows. Section 1 describes the local PRAM model, the data-flow graph representation and cost analysis. Following sections illustrate, using simple examples, the main techniques involved in the building of:

- section 2: a coarse granularity algorithm from a fine grain optimal one;

- section 3: a fast optimal algorithm from a very fast but non optimal one;

- section 4: a very fast optimal randomized algorithm from a deterministic but non optimal one.

Finally, in the last section, we give an overview of parallel time complexity, focusing on booleanarithmetic circuits which are commonly used in computer algebra.

### 1.1 PRAM, DFG and cost analysis

The Parallel Random Access Machine (PRAM) [18, 4] is the most common execution model used to build and analyze parallel algorithms. Its major feature is to be independent from the number of processors used. In this section we focus on the local PRAM model introduced in [38]. Cost analysis takes into account both arithmetic and communication complexities.

In the following, A denotes an algorithm and  $A_n$  its restriction for input of size O(n).

### 1.1.1 The PRAM model

A Local Parallel Random Access Machine (PRAM) is set of:

- an (infinite) number of processors  $P_0, \ldots, P_N, \ldots$ , each indexed by an integer (*processor identifier* or pid in short). Each processor is a RAM (Random Access Machine [2]) and gets its own local memory which contains its own pid.

- a global (or shared) memory. Each processor can copy data from the global memory into its own local memory: this operation is called global read or read in short. Conversely, each processor can copy a data from its own local memory into the global one: this operation is a write operation.

Initially, the input data are available in global memory. At the end of the computation, the output data are also stored there.

- A program that consists in a finite sequence of RAM elementary instructions, extended by the global elementary (i.e. single word location) read and write instructions.

- a global clock that ensures a synchronous mode of computation. After initialization (first top), processors are ready to execute the first instruction of the program. At each top (or *step*), each processor executes the next RAM instruction in the program. Thus it performs either an elementary arithmetic operation within its local memory or an access to the shared memory (read or write).

The program terminates when processor with pid 0 executes the halt instruction.

Note that the program may contain branching instructions eventually depending on the pid value. Due to branching instructions, at a given top, processors may execute different instructions (Multiple Instruction Multiple Data – MIMD – type).

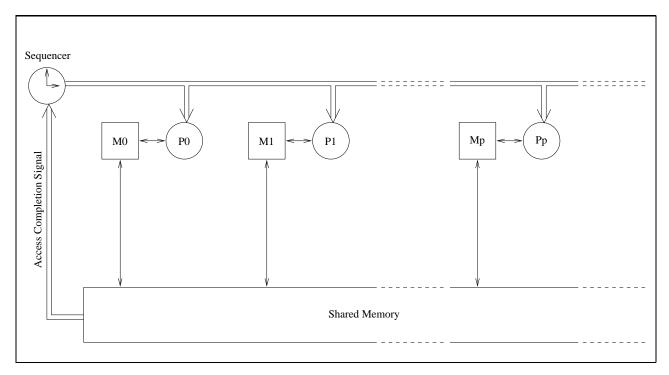

Figure 1.1: The local PRAM execution model

**Semantics of access in shared memory.** Due to the synchronous mode of computation, semantics of global memory access is simple and only depends on the behavior when, at a same top, several processors concurrently accede to a same single location in the shared memory.

At a same top, two processors can't perform both a read and a write in the same location. But concurrent read (or concurrent write) access may be allowed, depending on the PRAM:

• an EREW-PRAM (Exclusive Read Exclusive Write) does not allow concurrent access to a single location.

- a CREW-PRAM (Concurrent Read Exclusive Write) allows only concurrent read access.

- a CRCW-PRAM (Concurrent Read Concurrent Write) allows concurrent access (all in the same mode, either read or write).

When a concurrent write operation is performed into a single location in the shared memory, different semantics are considered depending on the reduction operation performed to produce the final value:

- COMMON: all processors have to write the same value. If not, an error is produced.

- ARBITRARY: an arbitrary processor writes its value.

- PRIORITY: the processor with the minimum pid writes its value.

- CUMULATIVE: the sum of all the concurrent values is written. The addition operation (defined between single location values) is assumed to be associative. Furthermore, it is assumed to be commutative; this ensures, a semantic independent from the pids of the writing processors likewise concurrent read and common or arbitrary write operations. This concurrent write mode is also called *combining* [41].

As detailed further, those different variants of the PRAM are relatively closed to each others: each one can simulate the other one with small overheads [14, 41, 28].

**Dynamic task creation** The above definition presents two drawbacks:

- it assumed that, after initialization, an unbounded number of processors start execution;

- dynamic creation of parallelism has to be described in the program using busy-waiting; this means that the scheduling of the program is completely described in the program.

In order to address this second point, in the initial definition from [18], only the processor with pid 0 starts execution of the program. To generate parallelism, an elementary fork  $\langle e \rangle$  instruction is defined. When a processor P executes this instruction, an inactive processor P' is reset. The accumulator of P (which may contain an address in the shared memory where some parameters are stored) is first copied into the one of P'. The pid of P' is then put into the accumulator of P. This allows P and P' to later communicate via the shared memory.

At the next step, P executes the following instruction (the one that follows the fork) and P' starts the execution of the program at the instruction labeled e.

Using fork, dynamic task creation is made possible, scheduling (allocation of inactive processors) being ensured by the PRAM machine. However, this modification implies that any PRAM program that uses a polynomial number  $n^{O(1)}$  of processors takes a time  $\Omega(\log n)$  to be executed, forbidding the building of constant time algorithms; if an algorithm is involved during the execution of a program (e.g. inside the body of a loop), this overhead may easily be avoided. Analysis of costs in this chapter are made under the previous model, thus without taking into account task allocation overhead.

**Randomized PRAM** To support execution of randomized algorithms, the PRAM is extended in the following way. A new random instruction is introduced that allows each processor to generate (in one top) a random bit (or a random number that fits in a single memory location).

Random generations (i.e. random instructions) performed by a processor during the execution are assumed to be independent realizations of an uniform law. Moreover, generations performed in parallel at a given top by different processors are also assumed to be independent.

### 1.1.2 Execution of a PRAM program and data-flow graphs

Being given the input data, the execution of a PRAM program may be represented as a direct acyclic graph. Vertices correspond to instructions that are executed (one vertex, one instruction) and edges to precedence relations between instructions.

Basically, due to the synchronicity of the PRAM, if v (resp. w) is the vertex representing an instruction executed<sup>1</sup> at step i (resp. i + 1), then there is an edge from v to w. If we forget extra synchronization due to the machine model, synchronizations required by the algorithm itself to ensure correctness of the execution correspond to the ordering of access into a location in memory. This ordering can be represented by the (macro) data-flow graph (DFG) related to the execution. DFG is direct acyclic and bipartite with node sets  $J = \{j_1, \ldots, j_n\}$  corresponding to instructions (j meaning job) and  $T = \{t_1, \ldots, t_m\}$  corresponding to single assignment data (t meaning transition). An edge goes from  $t_k$  (resp.  $j_i$ ) to  $j_i$  (resp.  $t_k$ ) if  $j_i$  is a read (resp. write) instruction of the global data related to  $t_k$ .

In this DFG, any memory access, either global or local, is represented by an edge between a location (represented by a transition node) and an instruction (a job node) that requires the access. Except for transitions related to input, immediate ancestors of each transition  $t_k$  are write instructions: only one on an exclusive-write PRAM, eventually more on a concurrent-write one. Conversely, its immediate successors (except for transitions related to output) are read instructions: only one on an exclusive prevent on a concurrent-read one. This means that when all immediate successors (job nodes) of a transition have been executed, the location related to it in global memory may be garbaged.

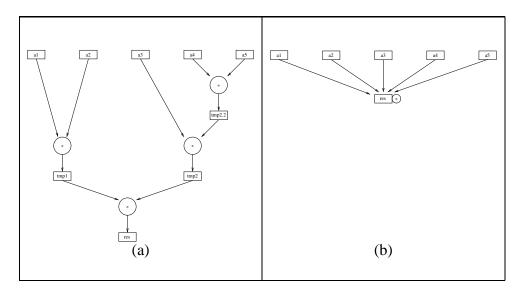

Let us consider the DFG related to a tree computation scheme. As an illustration, we consider two algorithms that solve the *iterated product*<sup>2</sup> problem: it consists in computing the product of n elements. In order to exhibit parallelism, multiplication is assumed to be associative and commutative. A balanced binary tree scheme gives an algorithm that works on an EREW PRAM; related DFG is shown in figure 1.2.a. On a CUMULATIVE-ERCW PRAM all products may be performed concurrently and cumulated on a shared location (fig. 1.2.b).

This graph defines a precedence relation, denoted  $\prec$ , between instruction nodes in J. Let  $j_1, j_2$  be two nodes in J;  $j_1 \prec j_2$  if there is a path in DFG from  $j_1$  to  $j_2$ . In the following, we will consider the subgraph  $DFG_a(J, \prec)$  of DFG, where only arithmetic instructions and their precedence relations are represented.

**Remark 1.** The data-flow description of the algorithm is roughly equivalent to a *straight-line program* [32].

<sup>&</sup>lt;sup>1</sup>Instructions corresponding to v and w may be executed by different processors.

<sup>&</sup>lt;sup>2</sup>also called *iterated sum* when an addition law is considered

Figure 1.2: DFG of two iterated products: (a) EREW (b) cumulative-ERCW

**Remark 2.** Note that symmetry of input (resp. output) edges to a transition node assumes commutativity of access. This is verified for any concurrent write (resp. read) access defined on the PRAM.

### **1.1.3 Describing PRAM algorithms: ATH language**

PRAM stands as an abstract model virtualizing any parallel architecture. In order to describe PRAM algorithms, we need an elementary programming language which leads to an easy description of algorithms.

Since the evaluation of a parallel algorithm is directly related to the analysis of DFG, a sequential description should be sufficient thanks to the implicit appearance of data-dependencies: each read access to a location gets the value put by the last write in a sequential execution. However, two characteristics, which do not appear in a sequential description, are to be taken into account:

- two levels of memory access are distinguished: local and global. Global memory access support CUMULATIVE-CRCW semantics.

- the elementary unit of instruction is the block. A block is a sequence of elementary RAM instructions. A block is executed in sequential; it takes benefit of local access.

In the following, we consider an extension of the basic PRAM basic language introduced in [18] based on those two considerations. This abstract language is called *ATH*, an acronym for *Asynchronous Tasks Handling*.

Blocks of instructions are defined as procedures bodies. The execution of such a block is called a *task*. Tasks may be ordered either in sequence using synchronous procedure call or in parallel using asynchronous procedure calls (prefixed by fork). In this last case, precedence relations between tasks are defined in a natural way, according to shared-data dependencies that appear in a sequential execution of the program. Data dependencies concerning local data are then not considered in the relative DFG.

Figure 1.3 gives two different recursive programs for the iterated product using a C++-like langauage. Version (a) works on an EREW PRAM and is related to the DFG presented in figure 1.2.a. Version (b) works on a CUMULATIVE-ERCW; the corresponding DFG is presented in figure 1.2.b.

```

Product(a : in E,

b : in E,

c : out E)

begin

c.Write( a.Read()*b.Read() );

end

IterProd( n

: in integer,

a[1..n] : in array of shared E,

: in integer,

IterProd( n

res : out shared E )

a[1..n] : in array of shared E,

begin

if(n==1)

: out shared E)

res

res.Cumul<*>( a[1].Read() );

begin

else

if(n==1)

res.Write( a[1].Read() );

fork IterProd( n/2, a[1..n/2], res );

else

fork IterProd( n-n/2, a[n/2+1..n], res );

tmpli, tmp2 : shared E;

end if

end

fork IterProd(n/2, a[1..n/2], tmp1);

fork IterProd(n-n/2, a[n/2+1..n], tmp2);

fork Product(tmp1, tmp2, res);

end if

end

(a)

(b)

```

Figure 1.3: ATH code of two iterated products: (a) EREW, (b) cumulative-ERCW. Data in shared memory are explicitly declared by the prefix shared. Notation x.f() means that function f is called on the data in shared memory x. In program (b), the function call x.Cumul < \* > (v) specifies a cumulative concurrent write on the data in shared memory x; the commutative and associative binary function implementing the operation is \*.

### **1.1.4** Time, work and communication costs

Consider a PRAM program. In the following, n denotes the size of the input. The arithmetic cost is characterized by:

- the *parallel time* T(n) which corresponds to the number of executed steps;

- the arithmetic work  $W_a(n)$ , i.e. the whole number of operations performed.

Those quantities are independent of the number of processors and thus may be defined directly from the DFG description of the execution.

**Definition 1** The parallel time T(n) is the maximal depth of DFG(x) for any input x of size n:

$$T(n) = \max_{x, ||x||=n} Depth(DFG_a(x))$$

(1.1)

The arithmetic work  $W_a(n)$  is the number of instruction nodes of DFG(x) for any input x of size n:

$$W_a(n) = \max_{x, ||x||=n} \#V(DFG_a(x))$$

(1.2)

The arithmetic cost is denoted:

$$O_a(T(n), W_a(n)) \tag{1.3}$$

Similarly, the communication cost is characterized by two factors:

- the *communication delay*<sup>3</sup>  $C_d(n)$ , i.e. the maximal number of global memory access performed by a processor;

- the communication work  $W_c(n)$ , i.e. the whole number of global memory access performed.

The PRAM program implements a scheduling of the DFG on an infinite number of processors: any access to the local memory on each processor is not considered as a communication. Thus, the communication cost may vary depending on the number of processors used in the program.

To define communication cost with respect to a parallel algorithm (independent of a number of processors, and so more general than the program that implements it), we will refer to its DFG.

**Definition 2** The communication work  $W_c(n)$  is the maximal number of edges for any input of size n:

$$W_c(n) = \max_{x, ||x||=n} \# E(DFG(x))$$

(1.4)

The communication delay  $C_d(n)$  is the maximal length of a path in DFG from an input data to an output one:

$$C_d(n) = \max_{x, ||x||=n} Depth(DFG(x))$$

(1.5)

The communication cost is denoted:

$$O_c(C_d(n), W_c(n)) \tag{1.6}$$

In order to compare arithmetic and communication costs, the granularity g(n) is defined.

**Definition 3** The granularity g(n) is the ratio between the arithmetic and communication works:

$$g(n) = \frac{W_a(n)}{W_c(n)} \tag{1.7}$$

**Remark.** Previous costs are defined at for DFGs with unit time instructions and unit size transitions. For general non unit size DFGs (denoted as macro data-flow graphs), costs are weighted by the size of each node: either the number of elementary instructions for a job node or the size of related data for a transition node. Macro data-flow graphs will be specifically studied in chapter 2.

$<sup>{}^{3}</sup>C_{d}(n)$  is called *communication complexity* in [28].

### 1.1.5 Efficient algorithms

Let  $\mathcal{A}$  be an algorithm with cost  $T(n), W_a(n), C_d(n), W_c(n)$ . Let  $W_s(n)$  be the work of the best known (sequential) algorithm that solves the same problem.

The building of a parallel algorithm to solve a given problem may be aimed at different directions:

- either finding the smallest amount of time required to solve a problem. In this context, the class NC of problems that may be solved in parallel time  $T(n) = \log^{O(1)} n$  using a polynomial number of processors  $W_a(n) = n^{O(1)}$  plays a central role.

- or building an *efficient* program that leads to solve larger problems in a reasonable amount of time taking benefit of the ability to use several processors, let us say p. Here, arithmetic and communication overheads (i.e.  $W_a(n)$  and  $W_c(n)$ ) are to be carefully taken into account in order to guarantee efficient executions.

A common trade-off [38] consists in building parallel algorithms that:

• have *polynomial speed-up*, i.e.

$$T(n) = O(W_s(n)^{\epsilon}) \quad \text{with } \epsilon < 1.$$

(1.8)

• are *work-preserving*, i.e.

$$W_a(n) = \Theta(W_s(n)). \tag{1.9}$$

The *inefficiency*  $\nu$  measures the arithmetic overhead:

$$\nu(n) = \frac{W_a(n)}{W_s(n)}.$$

(1.10)

• require few communications, i.e

$$W_{c}(n) = O(W_{a}(n)^{\epsilon}) \quad \text{with } \epsilon < 1.$$

(1.11)

Such an algorithm is also said *local* or *of coarse-granularity* or *with polynomial granularity* (note that  $g(n) = \Omega(n^{\alpha})$  with  $\alpha > 1$ ).

#### **Definition 4** A is said:

- fast if it achieves poly-logarithmic parallel time with a polynomial number of operations, i.e.  $T(n) = \log^{O(1)} n$  and  $W_a(n) = n^{O(1)}$ .

- optimal if it is fast and has constant inefficiency.

- efficient if it has a polynomial speed-up and a constant efficiency.

In order to not absolutely reject fast algorithms involving a small overhead in arithmetic operations, fast algorithms with poly-logarithmic inefficiency will be considered as efficient also. In the following, some main techniques that lead to the building of an efficient *and* of coarsegranularity algorithm are overviewed. It turns out that minimizing time without preserving work (i.e. building NC algorithm) is of specific interest:

- algorithmic techniques involved for both are very close;

- it gives a lower bound on the best parallel time that may be achieved;

- an inefficient but fast algorithm may successfully be coupled to a slower but efficient one to build a faster program.

### 1.1.6 Example

We illustrate the previous definitions on the iterated sum algorithm presented in figure 1.3.a. Scalar product of two vectors is directly reduced from iterated sum; it may be applied to perform matrix multiplication in a semi-ring.

#### **Iterated sum**

For the EREW algorithm presented in figures 1.3.a and 1.2.a (balanced tree computation scheme), we assume  $n = 2^m$ :

$$T(n) = \log n C_d(n) = \log n + 1 (1.12) W_a(n) = n - 1 W_c(n) = 2n - 1$$

This algorithm is optimal since its cost is – asymptotically – a lower bound.

As a consequence, the scalar product of two vectors is computed on an EREW with cost:

$$O_a(\log n, n)$$

and  $O_c(\log n, n)$ . (1.13)

On a semi-ring, + is commutative. Thus, on a cumulative-CRCW PRAM, this problem may be computed with parallel cost (fig. 1.2.a):

$$O_a(1,n)$$

and  $O_c(1,n)$ . (1.14)

However, the description of the computation scheme (cf program in fig. 1.3.b) may require  $O_a(\log n, n)$ .

#### **Matrix product**

Consider the problem of computing a square matrix product C = AB in a semi-ring (i.e. using only + and × operations).

Let *n* be the dimension of the matrices: since  $C_{i,j} = \sum_{k=1}^{n} A_{i,k} B_{k,j}$ , the problem reduces to  $n^2$  independent scalar products. Using 1.13, we obtain a parallel algorithm with cost:

$$O_a(\log n, n^3)$$

and  $O_c(\log n, n^3)$ . (1.15)

Since  $W_s(n) = \Theta(n^3)$  [37], this algorithm is efficient.

However, g(n) = O(1) and it is not coarse-granularity. Besides, it can be seen that, if E is a field (or ring), the above algorithm is not efficient (polynomial inefficiency) neither theoretically since  $W_s = O(n^{2.376})$  [15, 45] nor practically since  $O(n^{2.81})$  algorithms are of practical use [3, 40, 17]. We will see in following sections how to overcome those problems.

### 1.1.7 Relations between PRAMs

We consider the cost of the execution of a parallel algorithm (defined on a CUMULATIVE-CRCW PRAM for instance) on a given PRAM with a fixed number of processors and with its own semantics for access in shared memory. Two cases are distinguished: when the number of processors is decreased and when memory access are restricted. We consider here only arithmetic costs. The main consequence is the existence of optimal – within a constant factor – simulations of a CRCW algorithm that uses an unbounded number of processors on an EREW machine with a fixed number of processors.

**Theorem 1 Fine grain simulation with fewer processors - Brent's principle** [9, 28]. Let  $\mathcal{A}$  be an algorithm that can be implemented to run in (arithmetic) parallel time T and work  $W_a$  on a given PRAM with an unbounded number of processors. If each local access corresponds to a global one, then  $\mathcal{A}$  can be scheduled on the same PRAM, but with p processors, to run in (arithmetic) parallel time  $T_p(n)$ :

$$\left[\frac{W_a(n)}{p}\right] \le T_p(n) \le \left\lfloor\frac{W_a(n)}{p}\right\rfloor + T(n)$$

(1.16)

It can be noted that this fine grain simulation does not take into account additive cost due to the computation of the schedule [12, 22].

**Remark.** In chapter 2, theorem 10 gives a more general simulation result with analoguous bounds. It consists in a constructive coarse grain simulation for DFGs where arithmetic nodes may represent a sequence of elementary instructions.

**Theorem 2 Simulation with restricted access in global memory** [28, 38]. Let A be an algorithm that can be implemented to run in (arithmetic) parallel time  $T_p$  on a CUMULATIVE-CRCW PRAM with p processor. Then, A can be implemented on an EREW PRAM with p processors to run in time  $O(T_p \log p)$ .

### **1.2 Increasing granularity**

Efficient parallel algorithms require near-optimal work; obviously, the careful analysis of the smallest depth DFG induced by a sequential algorithm among the best is then of practical interest.

As a major example, sequential algorithms based on a partitioning of the problem into - many - independent subproblems have intrinsic parallelism if partitioning and merging (to recover the global solution) steps are either parallel or of neglected cost. This situation appears frequently in numerous divide&conquer algorithms (let us say *parallel divide&conquer*). As a computer algebra instance, modular methods based on Chinese remainder computations [2, 10] amount to this scheme.

Once a fine grain fast parallel algorithm is built, increasing granularity is required to obtain an efficient algorithm with coarse-granularity. In this section, the technique consisting in stopping the recursive splitting is illustrated on the matrix product problem; we prove an optimal granularity for this problem.

### 1.2.1 Parallel divide and conquer

Let us consider the example of matrix multiplication using a standard bi-dimensional block algorithm:

$$\begin{bmatrix} A_{11} & A_{12} \\ A_{21} & A_{22} \end{bmatrix} \begin{bmatrix} B_{11} & B_{12} \\ B_{21} & B_{22} \end{bmatrix} = \begin{bmatrix} A_{11}B_{11} + A_{12}B_{21} & A_{11}B_{12} + A_{12}B_{22} \\ A_{21}B_{11} + A_{22}B_{21} & A_{21}B_{12} + A_{22}B_{22} \end{bmatrix}.$$

(1.17)

All block matrices products, of dimension n/2, can be multiplied in parallel. Applying recursively this splitting scheme leads to a parallel algorithm with cost:

$$O_a(\log n, n^3) \quad O_c(\log n, n^3) \tag{1.18}$$

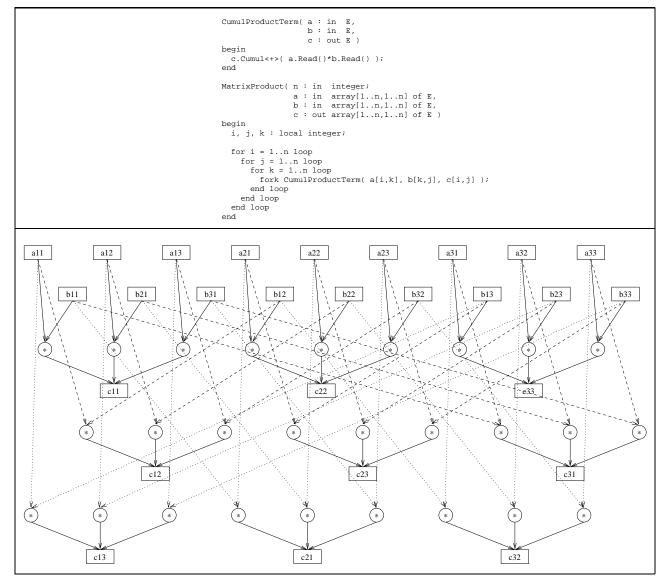

Note that, since coefficient addition is associative, each entry in the output matrix may be computed as an iterated sum of n values. This allows the whole computation to take a time  $\log n$  (instead of  $\log^2 n$  if additions where performed naively at each step). This remark appears directly on the DFG description for a CUMULATIVE-CRCW PRAM 1.4: all final sums are made in O(1) time. But the splitting process, which involves no arithmetic operation but recursive forks (cf fig. 1.3.b), requires  $O(\log n)$  time using recursive forks<sup>4</sup>. Another technique to obtain  $O_a(\log n, n^3)$  consists in pipelining additions [1].

**Remark.** The same strategy applied to Strassen's algorithm leads to a parallel algorithm with cost:

$$O_a(\log n, n^{\log_2 7}) \quad O_c(\log n, n^{\log_2 7})$$

(1.19)

Optimal in work (on a semi-ring), this algorithm has granularity g(n) = O(1): it is roughly equivalent to a recursive version of 1.15). In the next section, we detail how to increase granularity in order to build an efficient algorithm with coarse-granularity.

### 1.2.2 Minimizing communication work

Obtaining a coarse-granularity algorithm requires to minimize communications. This can be done by stopping the recursive parallel splitting process at a given depth, let us say when sub-matrices are of size lesser than k (i.e. depth  $\log \frac{n}{k}$ ). Operations – resp. sums and products – on matrices of dimension k are then performed sequentially, using an optimal algorithm – resp. in time  $O(n^2)$ and  $O(n^3)$  –. The cost is then:

$$O_a\left(k^3 + \log n, n^3\right) \quad O_c\left(k^2 + \log \frac{n}{k}, \frac{n^3}{k}\right) \tag{1.20}$$

which gives an algorithm with granularity g(n) = k. We thus obtain a parallel efficient algorithm with arbitrary (polynomial) granularity.

**Theorem 3** For any g,  $\log^{1/3} n \le g \le n$ , two  $n \times n$  matrices can be multiplied by an algorithm of granularity g with parallel cost:

$$O_a\left(g^3, n^3\right) = O_c\left(g^2 + \log n, \frac{n^3}{g}\right).$$

<sup>&</sup>lt;sup>4</sup>Note that the brute force program (fig. 1.4) which performs iteratively fork instructions requires  $O_a(n^3, n^3)$  !

Figure 1.4: DFG of the multiplication of two  $3 \times 3$  matrix (cumulative-CRCW)

The previous algorithm 1.20 proves the upper bound.  $\Box$ .

The following theorem gives lower bounds for communication costs. It shows that the previous algorithm achieves an optimal communication delay and an optimal granularity among algorithms that achieve an optimal communication delay.

**Theorem 4** Let A be an efficient parallel algorithm that multiplies two matrices of dimension n in time T using  $(+, \times)$  only and performing  $\Theta(n^3)$  operations. Then,

$$C_d = \Omega\left(T^{2/3} + \log n\right) \qquad W_c = \Omega\left(\frac{n^3}{C_d^{1/2}}\right)$$

Since  $\mathcal{A}$  is efficient,  $T = O(n^{\epsilon})$  with  $\epsilon < 3$ ; by reduction from iterative sum, we thus have  $C_d = \Omega(\log n)$ .

Kerr [37, 1] shows the lower bound  $\Omega(n^3)$  on the arithmetic work. Since  $\mathcal{A}$  performs  $\Theta(n^3)$  operations, its execution can be scheduled in time  $\Theta(T)$  using  $p = \frac{n^3}{T}$  processors. Let  $s_i, 1 \le i \le p$ , be the number of shared memory access performed by processor *i*. We then have  $W_c = \sum_{i=1}^p s_i$  and  $C_d \ge \max_{i=1}^p s_i$ . To obtain a lower bound on  $W_c$  and  $C_d$ , we use the following lemma [1, 25]: if a processor reads at most *s* elements of input matrices and computes at most *s* partial sums of their product, then this processor can compute no more than  $s^{3/2}$  multiplicative terms for these partial sums.

Applying this lemma to  $p_i$  which reads or writes at most  $s_i$  elements and since  $\Omega(n^3)$  multiplicative terms are to be computed, we have:

$$\sum_{i=1}^{p} s_i^{3/2} = \Omega(n^3).$$

(1.21)

Bounding  $s_i$  by  $C_d$  and replacing p by  $\frac{n^3}{T}$  leads to:

$$C_d = \Omega\left(T^{2/3}\right). \tag{1.22}$$

Noticing that  $\sum_{i=1}^{p} s_i^{3/2} \leq C_d^{1/2} \sum_{i=1}^{p} s_i$ , we obtain:

$$W_c = \Omega\left(\frac{n^3}{C_d^{1/2}}\right) \tag{1.23}$$

which concludes the proof  $\Box$ .

**Recursive multiplication algorithms.** A similar study can be applied to other recursive matrix multiplication algorithms (e.g. Strassen). It also lead to efficient parallel algorithms with both polynomial speed-up and polynomial granularity that lead to performant implementations [17].

#### 1.2.3 Conclusion

In this section, we have studied the DFG of a sequential algorithm, based on a divide&conquer scheme, that contains inherent parallelism. By halting the recursive process in order to minimize communications, we have exhibited a family of efficient parallel algorithms with arbitrary coarse-grain granularity.

Due to its practical interest, this technique has been successfully applied to various problems. One of significant interest in computer algebra is the discrete Fourier transform. The direct analysis of the FFT algorithm leads to a parallel algorithm with cost:

$$O_a(\log n, n \log n) \quad O_c(\log n, n \log n).$$

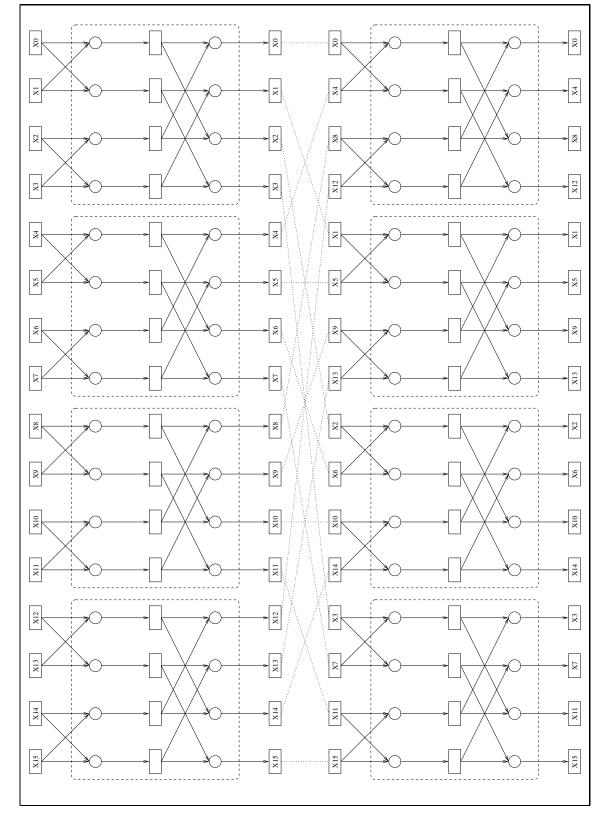

A clustering of elementary instructions (block clustering on the first  $\frac{\log n}{2}$  steps and cyclic clustering on the last  $\frac{\log n}{2}$  steps, cf fig. 1.5) leads to an algorithm with parallel cost [41, 39]:

$$O_a(\sqrt{n}\log n, n\log n) \quad O_c(\sqrt{n}, n).$$

This algorithm has polynomial speed-up, optimal work and achieves also optimal granularity [1].

Figure 1.5: DFG of the EREW  $O_a(\sqrt{n} \log n, n \log n)$  FFT algorithm of 16 points. There are  $2\sqrt{n}$  arithmetic tasks (represented by square boxes embedding elementary operations and local dependencies), each corresponding to a sequential FFT computation on  $\sqrt{n}$  points. For any task on the left, shared data dependencies imply a precedence relation with the  $\sqrt{n}$  tasks on the right.

The resulting algorithm is based on coupling a very fast parallel algorithm, optimal in time but requiring many communications, to a sequential one which minimizes communication. Such an algorithm is called "poly-algorithm"; the technique that underlies this coupling is called "cascading divide&conquer".

Cascading divide&conquer may be applied in a more general context, by coupling a very fast parallel algorithm, yet requiring many operations, to a slower one which performs an optimal number of operations. This technique makes the building of very fast algorithms attractive even if the required number of operations is larger.

### **1.3 Breaking data-flow dependencies by redundancy and cascading divide&conquer**

It may appear that DFGs related to a sequential algorithm contain data-dependencies that bound parallelism. Introducing redundant computations may then allow to break dependencies in order to minimize parallel time. Cascading divide&Conquer may then be used to obtain an optimal arithmetic work. In this section we illustrate this technique on the computation of the solution of a triangular linear system presented in [46]. We focus on communication costs.

Let A be an  $n \times n$  nonsingular triangular matrix with coefficients in a field K. We assume by convenience  $n = 2^m$ . Let b a vector in  $K^n$ . We consider the computation of  $x = A^{-1}b$ .

### **1.3.1** DFG of the best sequential algorithm

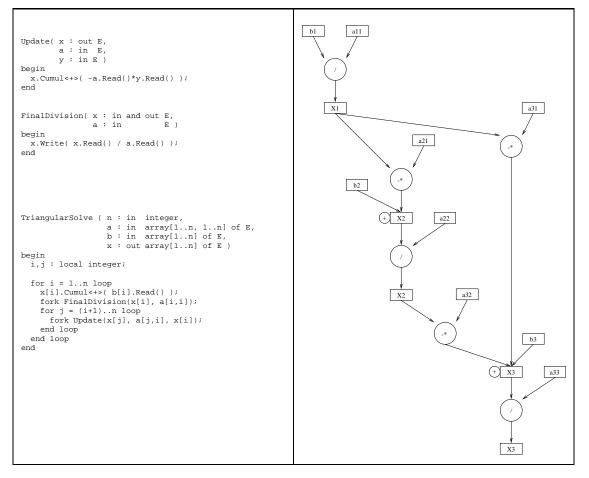

The simple forward substitution algorithm has sequential cost  $W_s(n) = \Theta(n^2)$ . Direct analysis of its DFG (see fig. 1.6) gives its parallel cost:

$$O_a(n, n^2) = O_c(n, n^2),$$

(1.24)

which leads to an algorithm with polynomial speed-up but small granularity g(n) = O(1).

If entries of A are in global memory after initialization, we have  $W_c(n) = \Omega(n^2)$ . In a view to minimizing the communications involved by the algorithm itself, in the following we do not consider the access to A in the communication work  $W_c(n)$ .

In order to increase granularity, we consider a divide&conquer version of this algorithm [7]. Let A, b and x be divided into blocks:

$$A = \begin{bmatrix} A_{11} & 0 \\ A_{21} & A_{22} \end{bmatrix} \qquad b = \begin{bmatrix} b_1 \\ b_2 \end{bmatrix} \qquad x = \begin{bmatrix} x_1 \\ x_2 \end{bmatrix}. \tag{1.25}$$

Here  $A_{11}$  is of size  $h \times h$ ,  $x_1$  and  $x_2$  are of size h. We have:

$$A_{11}x_1 = b_1$$

and  $A_{22}x_2 = b_2 - A_{21}x_1$ . (1.26)

where  $x_1$  and  $x_2$  are computed recursively using the same algorithm;  $A_{21}x_1$  is computed using a scalar product (see 1.13). Note that the use of a pipeline scheme leads to the previous parallel cost 1.24.

Figure 1.6: DFG for the solving of a  $3 \times 3$  nonsingular triangular matrix

We may then stop the recursive splitting when matrices are of size  $k \times k$ , and use sequential algorithms (triangular system inversion and matrix-vector product) on matrices of size lesser than k. The resulting parallel cost is:

$$O_a(nk, n^2) = O_c\left(nk, \frac{n^2}{k}\right)$$

(1.27)

which leads to an algorithm with granularity g(n) = O(k).

**Theorem 5** For any  $\epsilon < 1$ , a triangular nonsingular linear system can be solved by an efficient parallel algorithm of coarse granularity  $n^{\epsilon}$  in time  $O(n^{1+\epsilon})$ .

Choosing  $k = n^{\epsilon} = o(n)$  in 1.27 proves the upper bound.  $\Box$ .

### 1.3.2 Breaking dependencies

The linear time lower bound on previous algorithm time comes from the dependency in formula 1.26 between computations of  $x_1$  and  $x_2$ . This dependency may be broken by directly computing the inverses of the triangular nonsingular matrices  $A_{11}$  and  $A_{22}$ .

Consider the matrix A split in four blocks of dimension n/2 (1.25 with h = n/2). Then we have:

$$A^{-1} = \begin{bmatrix} A_{11}^{-1} & 0\\ -A_{22}^{-1}A_{21}A_{11}^{-1} & A_{22}^{-1} \end{bmatrix}$$

(1.28)

From theorem 3, the product of two matrices of dimension n is computed with parallel cost  $O_a(\log n, n^3)$ . In the following, we will refer to this cost.

To compute the inverse of A from 1.28, we first compute recursively and in parallel  $A_{11}^{-1}$  and  $A_{22}^{-1}$ . Then we compute the last block of  $A^{-1}$  by performing sequentially two parallel matrix products. The parallel cost for inverting A is then:

$$O_A(log^2n, n^3) = O_c\left(log^2n, \frac{n^3}{\log^{1/3}n}\right)$$

(1.29)

Once  $A^{-1}$  is computed,  $x = A^{-1}b$  can be computed with the same cost. However, even if polylogarithmic in time, this algorithm has polynomial inefficiency. In the next paragraph, we use it on  $A_{11}$  in 1.26 in order to decrease parallel time.

**Remark.** The above algorithm is efficient for computing the inverse of a nonsingular triangular matrix. Note that by using fast matrix multiplication, the parallel cost is reduced to  $O_a(\log^2 n, n^{\omega})$  with  $\omega < 2.38$  [46]. Besides, if computations are performed sequentially when the dimensions of the matrices are lesser than  $k \ge n^{\epsilon}$ , ( $\epsilon < 1$ ), the obtained algorithm is efficient and has polynomial speed-up and polynomial granularity.

#### **1.3.3** Cascading divide&conquer to minimize time

The previous algorithm is not efficient but may be combined to the recursive sequential algorithm (formula 1.26). The trick is to use it on small dimension matrices (let us say h) when the overhead  $O(h^3)$  due to the fast inversion of such a matrix becomes neglectible compared to coefficients updates (roughly nh). This leads to the following algorithm of Pan&Preparata [46].

**Theorem 6** The solution of a nonsingular triangular system can be computed in

$$O_a(n^{1/2}\log n, n^2)$$

using a standard  $n^3$  matrix multiplication algorithm. If a fast  $n^{\omega}$  multiplication is used then the parallel cost is:

$$O_a(n^{(\omega-2)/(\omega-1)}\log^2 n, n^2).$$

The following 1.27, let A be split in  $n^2/h^2$  blocks of size  $h \times h$ . Though, note that a direct computation (see theorem 1.27) leads to a parallel time  $O(n^{1/2} \log^2 n)$ . To avoid the  $\log n$  overhead factor in the parallel time, we proceed by gathering computation on  $\log^2 h$  blocks.

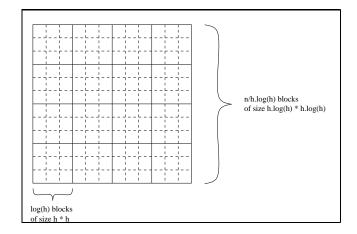

Let  $k = h \log h$ ; the matrix A may be seen as split in  $(n/k)^2$  blocks, each block consisting in  $\log^2 h$  sub-blocks of dimension h (cf fig. 1.7).

We use the sequential iterative algorithm on the  $(n/k) \times (n/k)$  coarse grain matrix. At step i, we

Figure 1.7: Splitting used for h = 8,  $h \log h = 24$ , n = 96

have to invert the triangular system corresponding to the diagonal block (i, i). For this computation, we first invert concurrently the  $\log h$  diagonal sub-blocks of this block. Then, we update others sub-blocks of  $x_i$ . At the end of the step, blocks  $x_j$ , for j > i, are updated. The algorithm is the following:

Initialization.

Let A be split into n/k blocks  $M_{i,j}$  of dimension k ( $k = h \log h$ ). For  $1 \le j \le i \le n/k$ , let  $M_{i,j}$  be split into  $\log h \times \log h$  block  $m_{i,j}^{k,l}$  of dimension h.

Let x be initialized to b and split according to A.

for i = 1..n/k do

- for j = 1.. log h do fork (m<sup>j,j</sup><sub>i,i</sub>)<sup>-1</sup> = invert(m<sup>j,j</sup><sub>i,i</sub>). Using fast inversion and Brent's principle, the cost is O<sub>a</sub>(log<sup>2</sup> h, h<sup>3</sup> log h).

- 2. for  $j = 1..\log h$  do update  $x_i^j$  in parallel  $x_i^j = \left(m_{i,i}^{j,j}\right)^{-1} \left(x_i^j - \sum_{l=1}^{j-1} m_{i,i}^{j,l} x_i^l\right)$

Scalar product are performed in parallel: thus  $x_i$  is computed with a cost  $O_a(\log^2 h, h^2 \log h)$ .

3. for j = i + 1..n/k fork update  $x_j$  in parallel  $x_j = x_j - M_{j,i}x_i$ Performing scalar product in parallel, the cost is  $O_a(\log h, nh \log h)$ .

The final cost is :  $O_a(n \log^2 h/k, n/k \max(h^3 \log h, nh \log h))$ . Since  $k = h \log h$ , it reduces to:

$$O_a(n\log h/h, \max(nh^2, n^2)),$$

and the optimal value for h is the larger one that leads to a work  $W_a(n) = O(n^2)$ . Thus, we choose  $h = n^{1/2}$  and we obtain the upper bound.

The same technique is applied to obtain the upper bound when a fast matrix multiplication algorithm is used.  $\Box$

### 1.3.4 Applications in linear algebra

Many linear algebra algorithms are based on a Gaussian elimination scheme: linear system solving, normal forms (Hessenberg, Smith, Frobenius, symbolic Jordan). Such a scheme provides parallel algorithms with polynomial speed-up: at each step, a transformation is computed that can then be applied in parallel to each coefficient of the matrix. For instance, solving a non-singular linear system using standard Gaussian elimination leads to a parallel algorithm with cost:

$$O_a(n, n^3) = O_c(n, n^2)$$

(1.30)

Moreover, very fast deterministic algorithms (polylogarithmic parallel time) are known for most problems [45, 24, 58, 57] but they are often inefficient ( $W_a(n) = n^{O(1)}W_s(n)$ ). For instance, solving a non-singular linear system can be computed in parallel with cost:

$$O_a(log^2n, n^{3+\alpha}) \tag{1.31}$$

with  $\alpha = 1/2$  in characteristic zero [16, 50] and  $\alpha = 1$  in the general case [11]. Applying the same cascading divide and conquer strategy leads to sub-linear parallel algorithms with optimal<sup>5</sup> work [46]:

$$O_a(n^{1/5}\log^2 n, n^3). \tag{1.32}$$

**Remark.** The same technique applied on Strassen formulation [56] (which may take benefit of fast  $O(n^{2.376})$  matrix multiplication algorithms), does not succeed in the building of a sub-linear algorithm with parallel time  $n^{\beta}$ ,  $\beta < 1$ .

#### 1.3.5 Conclusion

In this paragraph, we have used bi-dimensional block matrix partitioning in order to:

- increase the granularity to build polynomial speed-up algorithms with polynomial granularity; the technique used is cascading divide and conquer with a sequential algorithm in order to decrease communication costs.

- decrease parallel time while preserving the work; the technique used is cascading divide and conquer with a very fast but inefficient algorithm in order to make the computation faster.

In [46], the same technique, called *work-preserving speed-up*, is applied to several linear algebra algorithms: LU factorization, inversion, quasi-inversion, solution of linear structured systems.

<sup>&</sup>lt;sup>5</sup>relatively to the standard  $O(n^3)$  sequential algorithm

### **1.4** Randomization to decrease time or preserve work.

When an algorithm has a bounded degree of parallelism or a polynomial efficiency, randomization may help in order to either decrease time or preserve work, eventually both. This section illustrates both aspects on the computation of the rank of a matrix.

In computer algebra, randomization is most often introduced via the verification of a polynomial identity by evaluation on a random value. Testing whether a polynomial is identically zero can deterministically be solved by evaluating the polynomial, represented as a straight-line program, at a sufficient number of points. However, depending on the degree and on the number of indeterminates, such a deterministic test can require a huge number of evaluations. Following theorem, due to Schwartz [54], uses randomization in order to reduce this number while bounding the probability of failure.

**Theorem 7** [54, 28] Let  $P(x_1, ..., x_n)$  be a polynomial in the variables  $(x_i)$ ,  $1 \le i \le n$ , over a field K. Let I be a finite subset of K with cardinal c. Let  $(\alpha_1, ..., \alpha_n)$  be a vector selected at random in  $K^n$ . If P is not identically zero then

$$Prob\left(P(\alpha_1,\ldots,\alpha_n)\right)=0\right)\leq \frac{deg(P)}{c}.$$

Once a problem is reduced to the verification of a polynomial identity, this theorem allows to build a Monte-Carlo algorithm to solve it (for an introduction on Monte-Carlo and Las Vegas algorithms, see [36]). It is sufficient to build a parallel algorithm that evaluates the polynomial at a given input point. By choosing this point at random in a large enough finite subset<sup>6</sup> we obtain a Monte-Carlo algorithm whose probability of error is at most 1/2. This technique may be applied in a very large framework [36, 28] and is commonly used in computer algebra [45] to build fast algorithms with optimal work. We illustrate it on the problem of computing the rank of a matrix.

In the following, A denotes a matrix of dimension  $n \times n$  with coefficients in a field K. For the sake of simplicity, K is assumed infinite.

### **1.4.1** Randomization to suppress dependencies

The rank of a matrix can be computed using a standard pivoting Gaussian elimination. Similarly to 1.24, this results in an algorithm with parallel cost:

$$O_a(n, n^3) = O_c(n, n^2)$$

(1.33)

On the contrary to triangular system solving, the computation scheme (DFG) is relatively unknown: coefficients to modify are determined at each step only once the pivot element has been chosen.

In [8], randomization is used in order to reduce the whole problem to a fixed DFG on which parallelization techniques can be applied. The algorithm is based on the following characterization of the rank:  $\operatorname{rank}(A) = r$  iff there exist two non-singular matrices L and C such that the principal minor of dimension r in LAC is non zero while principal minors of dimension larger than r are

<sup>&</sup>lt;sup>6</sup>Note that, if K is not large enough, this may require to work in an extension of K [24].

zero. Moreover, L and C can be taken at random with a high probability of success: the use of theorem 7 to evaluate this probability requires to express the problem as a polynomial identity.

Let  $\delta_i(L, C)$  denote the principal minor of dimension *i* of *LAC*. Due to multi-linearity of the determinant,  $\delta_i$  is a polynomial of degree 2n with indeterminates  $L_{i,j}$  and  $C_{i,j}$   $(1 \le i, j \le n)$ . Previous rank characterization leads to the following polynomial identities:

$$\begin{aligned}

\delta_i &\neq 0 & 1 \le i \le r \\

\delta_i &= 0 & r < i \le n

\end{aligned}$$

(1.34)

This suggests the following Monte-Carlo algorithm to compute *r*:

- 1. Choose two random non-singular matrices L and C with coefficients in a finite subset of cardinal c of K;

- 2. Compute: M = LAC;

- 3. For  $1 \leq i \leq n$ , compute  $d_i = \det(M_i)$  and let  $d_0 = 1$ ;

- 4. Return s = Max<sub>k=0,...,n</sub> {k/d<sub>k</sub> ≠ 0}.

(Note that step 3 and 4 may be replaced by a logarithmic search to compute s).

In any case,  $s \le r$ . The probability of error, which occurs when s < r, corresponds to executions where the evaluation  $d_r$  of polynomial  $\delta_r$  is zero although  $\delta_r$ , of degree 2n, is not identically zero. From theorem 7, this probability is bounded by  $\frac{2n}{c}$ . Choosing c = 4n results in a Monte-Carlo algorithm with probability of error lesser than  $\frac{1}{2}$ .

Arithmetic cost is dominated by the computation of the n determinants. If Chistov's method [11] is used, this cost is:

$$O_a(log^2n, n^{\omega+1}) \tag{1.35}$$

In order to improve efficiency, determination of s may be computed using a logarithmic scheme instead of the previous brute force method. Using an efficient randomized algorithm to compute the determinant (for instance the randomized one of Kaltofen and Pan [33], the parallel cost becomes

$$O_a(\log^3 n, n^\omega \log n), \tag{1.36}$$

From Monte-Carlo to Las Vegas. The building of a Las Vegas algorithm from a Monte-Carlo one mainly consists in verifying that the output is a correct solution to the initial problem. Such a verification is easy from the previous algorithm; it suffices to verify that all columns (resp. rows) of the matrix M = LAC are linear combinations of s independent columns (resp. rows) in M, s being the output of the algorithm.

Consider the following splitting for M, the first block  $M_{11}$  being of size  $s \times s$ :

$$M = \begin{bmatrix} M_{11} & M_{12} \\ M_{21} & M_{22} \end{bmatrix}.$$

(1.37)

$M_{11}$  is a non-singular matrix. Let  $X = M_{21}M_{11}^{-1}$  and  $Y = M_{11}^{-1}M_{12}$ ; note that X and Y<sup>t</sup> are of size  $(n - s) \times s$ . Since L and C are non-singular, A is of rank s iff the last (n - s) rows and

columns of M are respectively linear combinations of the s first ones. This relies on the following identities:

$$\begin{cases} [M_{21} \ M_{22}] = X[M_{11} \ M_{12}] \\ \begin{bmatrix} M_{12} \\ M_{22} \end{bmatrix} = \begin{bmatrix} M_{11} \\ M_{12} \end{bmatrix} Y$$

$$(1.38)$$

Assuming a Las Vegas algorithm to compute  $M_{11}^{-1}$  with parallel cost  $O_a(\log^2 n, n^{\omega} \log n)$  ([33], those identities can be verified with a parallel cost:

$$O_a(\log^2 n, n^\omega \log n). \tag{1.39}$$

This results in an optimal randomized Las Vegas algorithm to compute the rank.

In the above algorithm, randomization is strongly used for preconditionning the input (computation on *LAC* instead of *A*) in order to suppress data dependencies that bounds parallelism. A natural question is then the existence of a fast deterministic algorithm, i.e. with few dependencies. In [44], Mulmuley provided such a deterministic algorithm for computing the rank: it achieves parallel time  $O(\log^2 n)$  but polynomial inefficiency. Then, randomization is required to provide efficiency.

#### **1.4.2 Randomization to provide efficiency**

Based on a generalization of a method developed in [27] for arbitrary fields, Mulmuley algorithm [44] reduces the problem of computing the rank to the computation of a characteristic polynomial in an extension of the ground field K.

In the following, A is assumed symmetric; this is done without loss of generality since

$$\operatorname{rank}(A) = \frac{1}{2}\operatorname{rank}\left(\left[\begin{array}{cc} 0 & A \\ A^t & 0 \end{array}\right]\right).$$

**Theorem 8** [44] Let A be a square symmetric matrix over a field K and let m be the highest integer such that  $x^m$  divides the characteristic polynomial  $\xi_{A_Z}(x) = \sum_{i=0}^n a_i(z)x^i$  of the matrix  $A_Z$  over K(z):

$$A_{Z} = \begin{bmatrix} 1 & & & \\ & z & & 0 \\ 0 & & \ddots & \\ & & & z^{n-1} \end{bmatrix} A.$$

Then rank(A) = n - m.

Deterministic parallel algorithms for computing the characteristic polynomial in parallel time  $O(\log^2 n)$  are known [16, 11] but they have work  $O(n^{\omega+1})$ . Even if we assume an optimal algorithm for computing the characteristic polynomial with arithmetic work  $O(n^{\omega})$ , due to polynomial arithmetic, the cost of the above algorithm would be:

$$O_a(\log^2 n, n^\omega n \log^{O(1)} n) \tag{1.40}$$

Since  $a_i(z)$  are polynomials of degree O(n), a way to obtain efficiency is to get rid off polynomial arithmetic on K using evaluation at a random value.

Moreover, efficient  $O_a(log^2n, n^{\omega} \log n)$  randomized algorithm are known for computing the minimal polynomial. Multiplying  $A_Z$  by a random non-singular matrix over K results, with high probability, in a matrix with distinct eigenvalues; then, minimal and characteristic polynomial are equal.

Those two steps of randomization result in the following efficient Monte-Carlo algorithm for computing the rank:

- 1. Choose a random non-singular matrix *P*;

- 2. Choose a random value z in K (or in an extension if K is too small);

- 3. Compute the minimal polynomial  $\xi_{PA_z}(x)$  of the matrix  $PA_z$ ;

- 4. Return n m where m is the highest integer such that  $x^m$  divides  $\xi_{PA_z}(x)$ .

The parallel cost is then:

$$O_a(\log^2 n, n^\omega \log n) \tag{1.41}$$

which results also in an efficient Monte-Carlo algorithm.

**Remark.** The above algorithm is very close to the one presented in 1.4.1; Mulmuley algorithm can effectively be considered as an inefficient deterministic version of 1.4.1. This is not surprising since both randomized algorithms solve efficiently the same problem. However, we have pointed out two different motivations for the use of randomization.

### 1.4.3 Conclusion

In the above examples, randomization is used to provide work-optimal computations from either slow or fast but not efficient deterministic algorithms. Due to the fact that only randomized algorithms are known for computing efficiently the inverse of a matrix in polylogarithmic time [33], randomization is an important tool in parallel computer algebra.

### **1.5** Parallel time complexity and NC Classification

An efficient parallel algorithm achieves polynomial speed-up within an optimal (or near optimal) number of operations. Obtaining bounds on the parallel time required to solve a given problem within a reasonable number of operations is then of fundamental interest. Moreover, as detailed in previous sections, very fast parallel but inefficient algorithms may be of practical interest if they can be coupled to an efficient but slow algorithm.

In the framework of parallel complexity, NC class [13] which includes polynomial sequential time problems that have a polylogarithmic parallel time plays an important role [35]. The parallel model used in the formal definition of NC is log-uniform family of boolean circuits [53].  $NC^k$  is the class of problems that can be solved by such a family with depth  $O(\log^k n)$  and  $n^{O(1)}$  boolean gates<sup>7</sup>. For instance, integer arithmetic (+, -, × and Euclidean division) lies in  $NC^1$ . Introduction

<sup>&</sup>lt;sup>7</sup>Gates compute bounded fan-in boolean operations (*or*, *and* and *not*) and have unbounded fan-out [26]. Extensions to unbounded fan-in gates leads to class AC [29].

of gates that deliver in output a random bit allows to define corresponding randomized classes: RNC for Monte-Carlo circuits and ZNC for Las Vegas ones. Problems *P*-complete [28, 49, 35] are in *NC* only iff NC = P; among them, the *monotone circuit value problem* (MCVP) consists in the evaluation of a boolean circuit, roughly equivalent to a DFG with boolean nodes as defined in this chapter. The integer greatest common divisor remains an open question; only sub-linear  $O(\frac{n}{\log n})$  algorithms are known [34, 35].

The algebraic extension [61] of this primitive model allows to build circuits which gates compute arithmetic operations in an algebraic domain. A gate testing nullity (? = 0) is introduced in order to mix boolean and arithmetic operations. For instance  $NC_F^k$  (F stands for *field*) is the class of problems that can be solved by log-uniform family of circuits whose gates perform arithmetic operations in any field, i.e. +, -, ×, / and ? = 0. Complexity of basic computer algebra problems has been extensively studied [8, 13, 59, 60, 35, 45]. Polynomial arithmetic (+, -, × and Euclidean division) lies in  $NC_F^1$  [45]. An important class is  $DET_F$  which contains problems  $NC^1$ -reducible to the determinant of a matrix; matrix powering is complete for  $DET_F$ .  $DET_F$ is included in  $NC_F^2$ . Most of linear algebra problems lie in  $NC_F^2$ : rank, null-space, minimal and characteristic polynomial, gcd of many polynomials [8, 44], Hermite normal form of polynomial matrices [31], Smith and symbolic Jordan forms [52, 58, 57, 21]. Note that those problems admit an optimal  $O_c(\log^2 n, W_s(n))$  parallel algorithm by using randomization [33, 23, 24, 45]. Though, in certain cases, some general techniques are known to remove randomness without increasing the work [42], no work optimal deterministic algorithms with poly-logarithmic time are known for those problems.

As it appears for most computer algebra problems studied in this chapter, parallel algorithms often appear as a restructuration of sequential ones, taking into account algebraic properties of the arithmetic operations involved. Although evaluation of a boolean circuit is *P*-complete, several algorithms have been developed to evaluate arithmetic DFGs (also called straight-line programs) taking benefit of the underlying structure. In a semi-ring, DFG that are trees can be evaluated in  $O(\log n)$  time without increasing the number of operations performed [9]. Any DFG performing *n* operations in a semi-ring and whose outputs are of arithmetic degree<sup>8</sup> *d* can be evaluated in  $O_a(\log n \log(nd), n^3)$  [32]. This result has been extended to DFGs performing operations in a lattice [51]. A more general simulation of a RAM machine on a PRAM one [43] shows that any DFG can be evaluate in parallel on an unbounded number of processors with polynomial speed-up.

### **1.6** Conclusion

This chapter overviews the PRAM framework (execution model and main algorithmic techniques) in which parallel algorithms are built and analyzed. The macro data-flow graph (DFG) related to the execution plays a central role: it describes data-dependencies between blocks of instructions.

Abstract measures used to analyze algorithms are *depth* and *work*; *arithmetic* and *communication* costs are distinguished. The one corresponds to operations performed (macro-instructions nodes) while the other to access in the shared memory (data dependencies nodes). Arithmetic work and depth have been used for many years to analyze performances of parallel algorithms

<sup>&</sup>lt;sup>8</sup>In such a DFG, any output may be equivalently seen as a polynomial whose indeterminates are the inputs. The arithmetic degree is then the maximal degree of polynomials corresponding to the outputs.

[9, 55, 35, 28, 6]. Due to experimental constraints, the relevance of communications costs (i.e. total communication traffic – work - and total communications delay) has been pointed out to obtain practical performant programs [5, 19]. Since minimizing communications overhead and minimizing parallel time are antagonist, good trade-offs have been studied for several common algorithms [47, 1, 48]. The granularity, defined as the arithmetic-to-communication works ratio, appears as a good parameter.

## **Bibliography**

- [1] A. Aggarwal, A. Chandra, and M. Snir. Communication complexity of PRAM's. *Theoretical Computer Science*, 71:3–28, 1990.

- [2] A. Aho, J. Hopcroft, and J. Ullman. *The design and analysis of computer algorithms*. Addison-Wesley, 1974.

- [3] D. Bailey. Extra high-speed matrix multiplication on the cray-2. *SIAM J. Sci. Sta. Comput.*, 9:603–607, 1988.

- [4] J. L. Balcázar, J. Díaz, and J. Gabarró. Structural Complexity II. Springer-Verlag, Berlin, 1990.

- [5] D. Bertsekas and J. Tsitsiklis. *Parallel and distributed computation*. Prentice-Hall, New York, 1989.

- [6] G. E. Blelloch. Programming Parallel Algorithms. *Communications of the ACM*, 39(3):85–97, 1996.

- [7] A. Borodin and I. Munro. *The Computational Complexity of Algebraic and Numeric Problems*. Elsevier, New-York, 1975.

- [8] A. Borodin, J. von zur Gathen, and J. Hopcroft. Fast parallel matrix and gcd computations. *Information and Control*, 52:241–256, 1982.

- [9] R. Brent. The parallel evaluation of general arithmetic expressions. *Journal of the ACM*, 21:201–206, 1974.

- [10] T. Bubeck, M. Hiller, W. Küchlin, and W. Rosentiel. Distributed symbolic computation with DTS. In *Proc. of IRREGULAR'95, Lyon, France*, pages 231–248. Springer-Verlag LNCS 980, Sep. 1995.

- [11] A. L. Chistov. Fast parallel calculation of the rank of matrices over a field of arbitrary characteristic. In *Proceedings of Fundamentals of Computation Theory*'85, pages 63–68. Springer-Verlag LNCS 199, 1995.

- [12] R. Cole and U. Vishkin. Approximate Parallel Scheduling. Part I : The Basic Technique with Applications to Optimal Parallel List Ranking in Logarithmic Time. *SIAM Journal on Computing*, 17(1), 1988.

- [13] S. Cook. A taxonomy of problems with fast parallel algorithms. *Information and Control*, 64:2–22, 1985.

- [14] S. Cook, C. Dwork, and R. Reischuk. Upper and lower time bounds for parallel random access machines with simultaneous writes. *SIAM Journal on Computing*, 15:87–97, 1986.

- [15] D. Coppersmith and S. Winograd. Matrix multiplication via arithmetic progressions. *Journal of Symbolic Computation*, 9:251–280, 1990.

- [16] L. Csánky. Fast parallel matrix inversion algorithms. SIAM Journal on Computing, 5:618– 623, 1976.

- [17] B. Dumitrescu, J.-L. Roch, and D. Trystram. Fast matrix multiplications algorithms on mimd architectures. *Parallel Algorithms and Applications*, 4(2), 1994.

- [18] S. Fortune and J. Wyllie. Parallelism in random access machines. In *Proceedings of the 10th ACM Symposium on Theory of Computing*, pages 114–118, San Diego, CA, 1978. ACM Press.

- [19] I. Foster. Designing and Building Parallel Programs: Concepts and Tools for Parallel Software Engineering. Addison-Wesley, Reading, MA, 1995. http://www.mcs.anl.gov/dbpp.

- [20] K. A. Gallivan, R. Plemmons, and A. H. Sameh. Parallel Algorithms for Dense Linear Algebra Computations. *SIAM Review*, 32(1), 1990.

- [21] T. Gautier and J.-L. Roch. NC<sup>2</sup> computation of a gcd-free basis and application to parallel algebraic number computations. In E. Kaltofen, editor, *Parallel Symbolic Computation* (PASCO'97), 1997.

- [22] T. Gautier, J.-L. Roch, and G. Villard. Regular versus irregular problems and algorithms. In Proc. of IRREGULAR'95, Lyon, France, pages 1–26. Springer-Verlag LNCS 980, Sep. 1995.

- [23] M. Giesbrecht. Fast algorithms for matrix normal forms. In *33rd IEEE Symposium FOCS*, *Pittsburgh*, pages 121–130, 1992.

- [24] M. Giesbrecht. Nearly optimal algorithms for canonical matrix forms. PhD thesis, University of Toronto, Department of Computer Science, Canada, 1993.

- [25] J. W. Hong and H. T. Kung. I/O complexity: the red-blue pebble game. In *Proc. 13th ACM Annual Symposium on Theory of Computing*, pages 133–139, 1981.

- [26] H. Hoover, M. Klawe, and N. Pippenger. Bounding fan-out in logical networks. J. ACM, 31:13–18, 1984.

- [27] O. Ibarra, S. Moran, and L. E. Rosier. A note on the parallel complexity of computing the rank of order *n* matrices. *Information Processing Letters*, 11:162, 1980.

- [28] J. Jájá. An Introduction to Parallel Algorithms. Addison-Wesley, Reading, Massachussets, 1992.

- [29] D. Johnson. A Catalog of Complexity Classes. In J. van Leuwen, editor, *Algorithms and Complexity*, pages 67–161. Elsevier, 1990.

- [30] E. Kaltofen. Parallel algebraic algorithm design. Technical report, Rensselaer Polytechnic Institute, 1989. Lecture notes for a tutorial, ISSAC'89.

- [31] E. Kaltofen, M.-S. Krishnamoorthy, and B. Saunders. Parallel algorithms for matrix normal forms. *Linear Algebra and its Applications*, 136:189–208, 1990.

- [32] E. Kaltofen, G. Miller, and V. Ramachandran. Efficient parallel evaluation of straight-line code and arithmetic circuits. *SIAM Journal on Computing*, 17:687–695, 1988.

- [33] E. Kaltofen and V. Pan. Processor efficient parallel solutions of linear systems over an abstract field. In *Proc. Third Annual ACM Symposium on Parallel Algorithms and Architectures*, pages 180–191, Hilton Head, SC, 1991. ACM Press.

- [34] R. Kannan, G. Miller, and L. Rudolph. Sublinear parallel algorithm for computing the greatest common divisor of two integers. *SIAM Journal on Computing*, 16-1:7–16, January 1987.

- [35] R. Karp and V. Ramachandran. Parallel algorithms for shared-memory machines. In J. van Leuwen, editor, *Algorithms and Complexity*, pages 869–932. Elsevier, 1990.

- [36] R. M. Karp. An introduction to randomized algorithms. *Disc. Appl. Math.*, 34:164–201, 1991.

- [37] L. R. Kerr. *The effect of algebraic structure on the computational complexity of matrix multiplications.* PhD thesis, Cornell University, New-York, 1970.

- [38] C. P. Kruskal, L. Rudolph, and M. Snir. A complexity theory of efficient parallel algorithms. *Theoretical Computer Science*, 71:95–132, 1990.

- [39] V. Kumar, A. Grama, A. Gupta, and G. Karypis. Introduction to Parallel Computing: Design and Analysis of Algorithms. Benjamin Cummings, Redwood City, 1994.

- [40] J. Ladreman, V. Pan, and X.-H. Sha. On practical acceleration of matrix multiplication. *Linear Algebra and its Applications*, 1992.

- [41] F. T. Leighton. Introduction to Parallel Algorithms and Architectures: Arrays Trees Hypercubes. Morgan Kaufmann, New-York, 1992.

- [42] M. Luby. Removing Randomness in Parallel Computation without a Processor Penalty. J. Computer and System Sciences, 47:250–286, 1993.

- [43] L. Mak. Parallelism always help. SIAM Journal on Computing, 26(1):153–172, 1997.

- [44] K. Mulmuley. A fast parallel algorithm to compute the rank of a matrix over an arbitrary field. *Combinatorica*, 7(1):101–104, 1987.

- [45] V. Y. Pan and D. Bini. Polynomial and Matrix Computations I. Birkhauser, Boston, 1994.

- [46] V. Y. Pan and F. P. Preparata. Work-preserving speed-up of parallel matrix computations. *SIAM Journal on Computing*, 24(4), 1995.

- [47] C. H. Papadimitriou and J. D. Ullmann. A communication-time tradeoff. SIAM Journal on Computing, 16:639–646, 1987.

- [48] C. H. Papadimitriou and M. Yannakakis. Towards an architecture-independent analysis of parallel algorithms. SIAM Journal on Computing, 19(2):322–328, 1990.

- [49] I. Parberry. Parallel Complexity Theory. Pitman, London, 1987.

- [50] F. P. Preparata and D. V. Sarwate. An improved parallel processor bound in fast matrix inversion. *Information Processing Letters*, 7:148–150, 1978.

- [51] N. Revol and J.-L. Roch. Parallel evaluation of arithmetic circuits. *Theoretical Computer Science*, 162:133–150, 1996.

- [52] J.-L. Roch and G. Villard. Fast parallel computation of the Jordan normal form of matrices. *Parallel Processing Letters*, 6(2):203–212, 1996.

- [53] W. Ruzzo. On uniform circuit complexity. J. Computer and System Sciences, 22, 3:365–383, 1981.

- [54] J. Schwartz. Fast Probabilistic Algorithms for Verification of Polynomial Identities. *J. ACM*, 27(4):701–717, 80 1980.

- [55] Y. Shiloach and U. Vishkin. An  $O(n^2 \log n)$  parallel Max-Flow algorithm. *Journal of Algorithms*, 3:128–146, 1982.

- [56] V. Strassen. Gaussian elimination is not optimal. Numerische Math., pages 354–356, 1969.

- [57] G. Villard. Fast parallel algorithms for matrix reduction to normal forms. Appli. Alg. Eng., Comm. Comp., to appear.

- [58] G. Villard. Fast parallel computation of the Smith normal form of polynomial matrices. In International Symposium on Symbolic and Algebraic Computation, Oxford, UK, pages 312 – 317. ACM Press, July 1994.

- [59] J. von zur Gathen. Parallel algorithms for algebraic problems. *SIAM Journal on Computing*, 13:802–824, 1984.

- [60] J. von zur Gathen. Parallel arithmetic computations : a survey. In *Proc. 12th Int. Symp. Math. Found. Comput. Sci., Bratislava*, pages 93–112. LNCS 233, Springer-Verlag, 1986.

- [61] J. von zur Gathen. Algebraic complexity theory. Ann. Rev. Comput. Sci., 3:317–347, 1988.

## Chapter 2

# **Programming models and scheduling**

### Contents

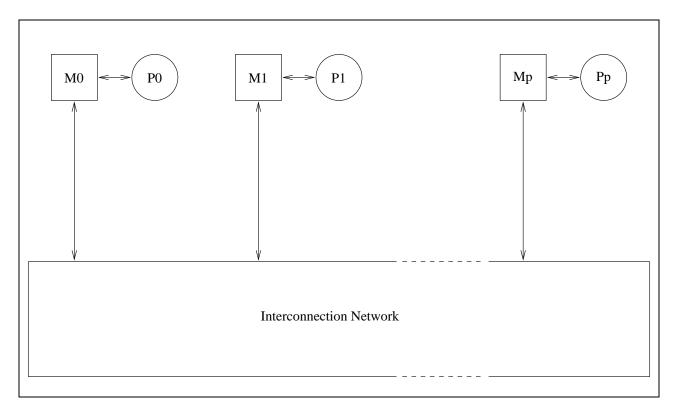

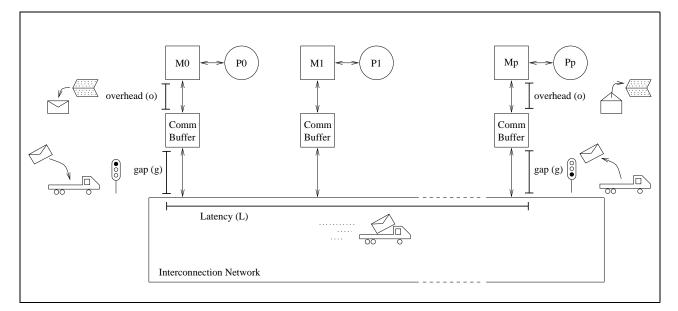

| 2.1 | Async  | hronous distributed architectures                 |

|-----|--------|---------------------------------------------------|

|     | 2.1.1  | Realistic models of distributed architectures     |

|     | 2.1.2  | Basic programming tools                           |

|     | 2.1.3  | Shared virtual memory                             |

| 2.2 | How t  | o schedule a DFG                                  |

|     | 2.2.1  | Scheduling cost of a DFG 39                       |

|     | 2.2.2  | Off-line and on-line scheduling 41                |

|     | 2.2.3  | Which scheduling algorithms in computer algebra?  |

| 2.3 | On-lin | e scheduling algorithms 43                        |

|     | 2.3.1  | Foundations of on-line scheduling                 |

|     | 2.3.2  | Lower bounds for competitive ratio                |

|     | 2.3.3  | Communications and scheduling overheads           |

|     | 2.3.4  | Athapascan: a simulation of the ATH PRAM language |

|     | 2.3.5  | The ATHAPASCAN programming model                  |

|     | 2.3.6  | Execution model of ATHAPASCAN                     |

|     | 2.3.7  | An example of ATHAPASCAN program                  |