Problèmes de Muntz, Goyal et Carrasco: présentation et modélisation par des RAS

A. Bušić and J. M. Fourneau

PRiSM, Université de Versailles

jmf@prism.uvsq.fr

Plan

- Cadre général

- Description du modèle

- Modélisation par des RAS

## Cadre général

Des problèmes de disponiblité pour des systèmes à plusieurs composants de types différents.

- Les composants de même type ne sont pas différentiés.

- Des pannes et des réparations

- simples ou multiples

- les pannes exponentielles, les réparations exponentielles ou PH

- une discipline de service pour les réparations

- les réparations peuvent être prioritaires

(en cas de PH, resume ou restart)

- il peut y avoir plusieurs réparateurs

- plusieurs modes de pannes (Soft, Hard); la réparation dépend du mode de la panne

- Représentation du système par le nombre de composants en panne dans chaque mode.

- Les états UP (système opérationnel) : un nombre minimal de composant en marche dans chaque type

- en grand nombre mais en très faible proportion par rapport au nombre total d'état (la chaine est très grande)

## Description du modèle

Muntz et al. 1989, Carrasco 1999

- Les composants

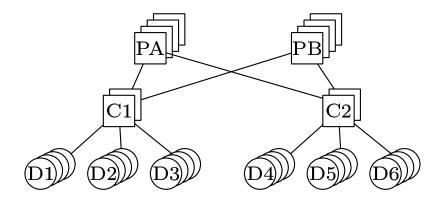

- Processeurs : 2 types (PA et PB) (attention : pas indépendants !) 4 processeurs de chaque type : un seul processeur par type fonctionne, les autres sont là en cas de pannes.

- Contrôleurs : 2 types (C1 et C2); 2 contrôleurs de chaque type.

- Disques : 6 piles de 4 disques. D1, D2 et D3 liées aux contrôleurs C1, et les piles D4, D5 et D6 aux contrôleurs C2.

#### • Les états UP:

- au moins un processeur en activité (PA ou PB)

- au moins un contrôleur en activité pour chaque type (C1 et C2)

- au plus un disque en panne par pile

- Les pannes et les réparations :

- 2 modes de pannes : Soft et Hard; pour chaque type de composant

- une seule réparation à la fois, le choix uniforme

- les pannes simples (un seul objet à la fois) sauf la panne du processeur PA qui peut entrainer la panne du processeur PB

- seul le processeur en activité peut tomber en panne

- les taux de pannes dépendent du type du composant et du mode de la panne

# Modélisation par des RAS

Attention : les fonctions sont de vraies fonctions et ne respectent pas la syntaxe de PEPS.

### Les processeurs

- Inactif, Actif, Panne Soft, Panne Hard

- suffisant de connaître le nombre de processeurs en Panne Soft et Panne Hard (par type)

Nombre de PA en activité : 1 si  $PA_{Soft} + PA_{Hard} \leq 3$ , 0 sinon. Nombre de PA inactif :  $(3 - PA_{Hard} - PA_{Soft})^+$ .

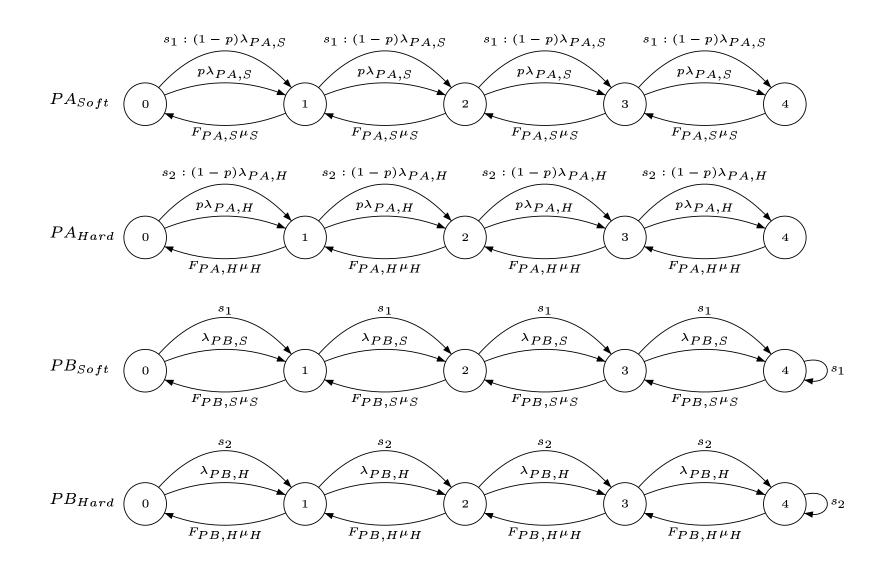

• 4 automates :  $PA_{Soft}$ ,  $PA_{Hard}$ ,  $PB_{Soft}$  et  $PB_{Hard}$ Chaque automate possède 5 états (de 0 à 4).

Les contraintes d'admissibilité:

$$PA_{Soft} + PA_{Hard} \le 4$$

et  $PB_{Soft} + PB_{Hard} \le 4$

$\rightarrow$  des taux fonctionnels.

Remarque: 15 configurations atteignables (parmi 25).

Utiliser un seul automate par type de processeur?

$$f(u,v) := 1_{u+v<4}$$

#### Les transitions:

- Les pannes simples de PA:

- Soft : une transition locale fonctionnelle de taux  $p\lambda_{PA,S}f(PA_{Soft},PA_{Hard})$ .

- Hard : une transition locale fonctionnelle de taux  $p\lambda_{PA,H}f(PA_{Soft},PA_{Hard})$ .

- Les pannes simples de PB

#### • Les pannes doubles

- Soft double (transition synchronisée) : une panne Soft sur PA qui provoque le même mode de panne sur B.

- Le taux :  $(1-p)\lambda_{PA,S}f(PA_{Soft},PA_{Hard})$ .

- Hard double (transition synchronisée) : une panne Hard sur PA qui provoque le même mode de panne sur B.

Le taux :  $(1-p)\lambda_{PA,H}f(PA_{Soft},PA_{Hard})$ .

Attention : les pannes doubles ne sont pas détaillées dans Muntz et Goyal, 1989.

Ici : une panne de PA provoque la panne du même type sur PB. Possible de considérer tout les quatre cas et leur probabilités. • Les réparations (transitions locales) :

Taux :  $F_{t,m}()\mu_m()$ , où

$-\mu_m$  = le taux de réparation du réparateur pour le type de panne m; varie selon que le système est UP ou DOWN.

$$\mu_m() = \mu_{m,UP}System() + \mu_{m,DOWN}(1 - System())$$

La fonction System() retourne 1 si le système est UP et 0 sinon.

$$System() = (1_{PA_{Soft}+PA_{Hard}+PB_{Soft}+PB_{Hard} \le 7}) \times (1_{C1 \le 2} \times 1_{C2 \le 2}) \times (\prod_{x=1..6} 1_{Dx \le 2})$$

$-F_{t,m}()$  = la probabilité de choisir une composante de ce type t et avec le mode de panne m.

NPanne(x,y) = le nombre de panne de type y sur la composante x.

Simple pour les processeurs, par exemple

$NPanne(PA, Soft) = PA_{Soft}.$

$$F_{PA,S}() = \frac{NPanne(PA, Soft)}{\sum_{x \in \{PA, PB, C1, C2, D1, \dots, D6\}} \sum_{y \in \{Soft, Hard\}} NPanne(x, y)}$$

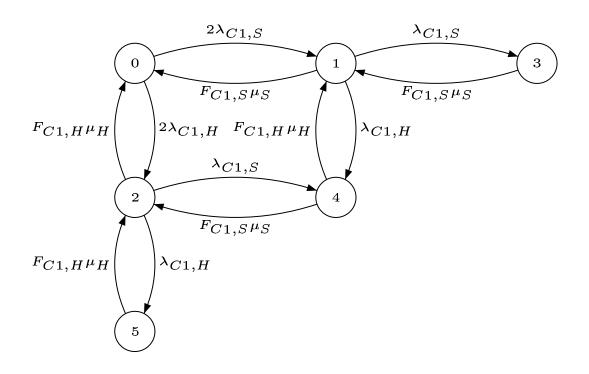

### Les contrôleurs

- Actif, Panne Soft, Panne Hard

- 2 automates (C1 et C2); les états (x, y) où x = nombre de pannes Soft, y = nombre de pannes Hard $\rightarrow 6 \text{ états: } (0, 0), (1, 0), (0, 1), (2, 0), (1, 1), (0, 2) \text{ (numérotés de 0 à 5)}$

4 transitions : réparations et pannes pour les modes Soft et Hard.

- Les pannes transitions locales de taux fixes. Le taux :  $\lambda_{t,m}$  où t = type de contrôleur, m =le type de panne.

- Les réparations transitions locales de taux fonctionnel Taux :  $F_{t,m}()\mu_m()$  avec

$$NPanne(C1, Soft) = 2 \times 1_{C1=3} + 1_{C1=1} + 1_{C1=4}$$

$$NPanne(C1, Hard) = 2 \times 1_{C1=5} + 1_{C1=2} + 1_{C1=4}$$

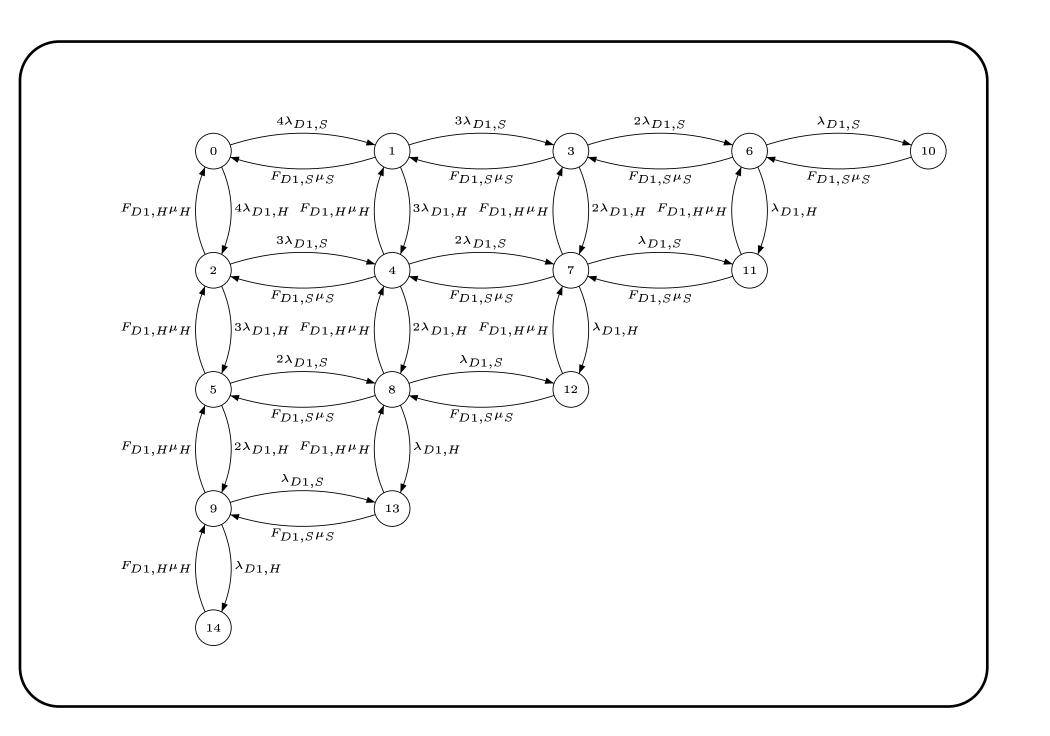

### Les disques

On modélise chaque pile isolée  $\rightarrow$  6 automates.

Etats : (x, y) où x =le nombre de panne Soft, y =nombre de panne Hard.

L'automate a 15 états numérotés de 0 à 14 :

| 0     | 1     | 2     | 3     | 4     | 5     | 6     | 7     |

|-------|-------|-------|-------|-------|-------|-------|-------|

| (0,0) | (1,0) | (0,1) | (2,0) | (1,1) | (0,2) | (3,0) | (2,1) |

| 8     | 9     | 10    | 11    | 12    | 13    | 14    |       |

| (1,2) | (0,3) | (4,0) | (3,1) | (2,2) | (1,3) | (0,4) |       |

Les pannes - des événements locaux et de taux fixe  $\lambda_{t,m}$  (t = la pile de disque, m = le type de panne).

Les réparations - des transitions locales de taux fonctionnels.

$$NPanne(D1, Soft) = 4 \times 1_{D1=10}$$

$+ 3 \times 1_{D1=6} + 3 \times 1_{D1=11}$

$+ 2 \times 1_{D1=3} + 2 \times 1_{D1=7} + 2 \times 1_{D1=12}$

$+ 1_{D1=1} + 1_{D1=4} + 1_{D1=8} + 1_{D1=13}$

$NPanne(D1, Hard) = 4 \times 1_{D1=14}$

$+ 3 \times 1_{D1=9} + 3 \times 1_{D1=13}$

$+ 2 \times 1_{D1=5} + 2 \times 1_{D1=8} + 2 \times 1_{D1=12}$

$+ 1_{D1=2} + 1_{D1=4} + 1_{D1=7} + 1_{D1=11}$

# Les valeurs numeriques des taux

Les deux types de panne (Soft et Hard) arrivent avec la même probabilité. Les valeurs numeriques des taux (en  $h^{-1}$ ):

$$\lambda_{t,S} = \lambda_{t,H} = 0.5\lambda_t, \forall t,$$

avec les constantes  $\lambda_t$ :

| $\lambda_{PA} = \lambda_{PB} = \lambda_{C1}$ | $\lambda_{C2}$ | $\lambda_{D1}$ | $\lambda_{D2}$ | $\lambda_{D3}$ | $\lambda_{D4}$ | $\lambda_{D5}$ | $\lambda_{D6}$ |

|----------------------------------------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

| 1/2000                                       | 1/4000         | 1/6000         | 1/8000         | 1/10000        | 1/12000        | 1/14000        | 1/16000        |

La panne du PA entraine la panne du PB avec la probabilité  $0.1\ (p=0.9).$

Les réparations sont 10 plus rapides quand le système est DOWN :

$$\mu_{m,DOWN} = 10\mu_{m,UP}, m \in \{Soft, Hard\}.$$

| $\mu_{Soft,UP}$ | $\mu_{Hard,UP}$ |

|-----------------|-----------------|

| 0.1             | 0.05            |

### Taille du problème

Sans regroupement pour les processeurs, on a un espace d'états produit de taille gigantesque obtenu comme suit:

• Pour les processeurs :  $5^4$

• Pour les contrôleurs : 6<sup>2</sup>

• Pour les disques : 15<sup>6</sup>

En utilisant un seul automate par type de processeur  $\rightarrow 15^2$  au lieu de  $5^4$  (tous les états atteignables).

La taille :  $6^2 \times 15^8$ , soit un peu plus de 92 milliards d'états.

Impossible de générer un tel modèle, même sur disque :

le degré moyen de  $11 \rightarrow 10^{12}$  transitions;

10 octets par transition (structure creuse)  $\rightarrow$  l'ordre de grandeur de  $10^{13}$  octets.

Faible pourcentage d'états UP :

- Pour un disque, il y a 3 états UP parmi les 15 états possibles

- Pour les contrôleurs, il y a 3 états UP parmi les 6 états possibles

- pas de réduction triviale pour les processeurs.

- $\rightarrow$ au plus  $15^2\times 3^2\times 3^6=1476225$ états UP

Sur les  $225 = 15^2$  états utilisés pour coder les deux ensembles de processeurs, 200 états correspondent à des états UP.

On a donc exactement 1300200 états UP (vérifié en générant la matrice pour une analyse de fiabilité)